## DIPLOMA PROJECT

# **Enhancing Genetic Search Efficiency for RRIP Cache Policies Across Diverse Workloads**

#### MARKO ZAKO

UNIVERSITY OF CYPRUS

DEPARTMENT OF COMPUTER SCIENCE

May 2025

# UNIVERSITY OF CYPRUS DEPARTMENT OF COMPUTER SCIENCE

# **Enhancing Genetic Search Efficiency for RRIP Cache Policies Across Diverse Workloads**

#### **MARKO ZAKO**

#### **SUPERVISOR**

Yiannakis Sazeides

The personal dissertation is submitted in partial fulfillment of requested obligations for receiving the degree of computer science from the department of Computer Science of the University of Cyprus

May 2025

# Acknowledgements

First and foremost, I want to thank my family for always being there for me. Their support, encouragement, and belief in me have meant everything throughout this journey. I wouldn't have made it this far without their constant presence and the sacrifices they made to give me the chance to study at a top university. I'll always be grateful for that.

Secondly, the support of my friends and classmates was what got me through these 4 years, their help and support always made me push through, even during the hardest days during this journey. I couldn't have asked for a better group to go through this experience with.

A special thank you to my supervisor, Mr. Yiannakis Sazeides, for his valuable guidance throughout the making of my thesis. His insight and advice were truly helpful and appreciated.

Lastly, I'd like to thank Ioannis Constantinou and Panteleimonas Chatzimiltis for always being willing to help whenever I ran into technical issues. Their support made a real difference.

## **Abstact**

Computers are getting faster, and programs are getting more demanding. With the introduction of Amdahl's law and Moore's law, we can observe that computational power is hitting a plateau. One of the fields that support this plateau and can be improved on is the field of cache replacement policies. The most critical level in the hierarchy is the LLC, which can save us many cycles if the needed information is stored there.

There are some policies such as LRU (PLRU) that have overall good performance, but we observe that there is room for improvement. State-of-the-art policies such as DRRIP [2] improve on the performance of LRU, but are still far off Belady's optimal policy. One issue with most of these policies is that they do not have an adaptation technique to a workload's pattern.

This thesis is expanding on continued work that looks at how we can use genetic algorithms to improve cache replacement policies for better performance across different workloads. We study how the results change when the genetic algorithm is run using a single benchmark compared to using a mix of benchmarks. This helps us understand which parts of a policy really matter for performance. We then proceed on finding the important functions on the benchmark's best performing policies, to see how achievable it is to find common ground for a policy for more than 1 benchmark. Finally, we try to find the smallest number of policies needed to get good performance across all benchmarks and test.

There are some promising results on isolating the workload, showing a good improvement on the search of the algorithm. There was an importance observed on the insertion function of a benchmark, while demotion functions were not as important. The policies produced for one benchmark were all different from policies for other benchmarks, showing their differences in behavior.

These results suggest that a one-size-fits-all policy is insufficient, and that using a small set of tailored policies can better match workload diversity and improve overall cache efficiency.

# **Contents**

| Chapter 1                             | 1  |

|---------------------------------------|----|

| Introduction                          | 1  |

| 1.1 Introduction                      | 1  |

| 1.2 Outline                           | 4  |

| Chapter 2                             | 6  |

| Background                            | 6  |

| 2.1 Modern CPUs                       | 6  |

| 2.1.1 Moore's Law                     | 8  |

| 2.1.2 Amdahl's Law                    | 9  |

| 2.2 Memory Hierarchy                  | 10 |

| 2.2.1 Cache Memory                    | 11 |

| 2.3 Cache Replacement Policies        | 13 |

| 2.4 Genetic Algorithm                 | 15 |

| 2.5 Microarchitectural Simulator      | 16 |

| Chapter 3                             | 17 |

| SRRIP-DRRIP                           | 17 |

| 3.1 SRRIP                             | 17 |

| 3.2 Set Dueling                       | 19 |

| 3.3 DRRIP                             | 20 |

| 3.4 Improving upon DRRIP              | 21 |

| Chapter 4                             | 22 |

| Frameworks and Methodology            | 22 |

| 4.1 HPC System                        | 22 |

| 4.2 ChampSim                          | 23 |

| 4.2.1 Cache Configuration             | 23 |

| 4.3 GeST                              | 24 |

| 4.3.1 The framework                   | 24 |

| 4.3.2 Configuring policies as genomes | 26 |

| 4.4 SPEC 2017 Benchmarks              | 30 |

| 1.1.1 The benchmarks                  | 30 |

| 4.5 Evaluation Methodology                                 | 32 |

|------------------------------------------------------------|----|

| Chapter 5                                                  | 34 |

| Workload experiments                                       | 34 |

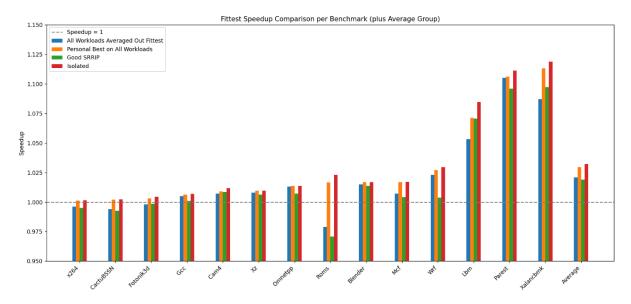

| 5.1 Isolated and averaged workloads                        | 34 |

| 5.1.1 Comparing isolated workload to averaged out workload | 36 |

| 5.1.2 Similarity between policies                          | 37 |

| 5.2 Finding the ideal policy pairs                         | 43 |

| 5.2.1 Similarity between workloads                         | 43 |

| 5.2.2 Minimum policies needed to cover all workloads       | 44 |

| 5.3 Finding an ideal crossover point                       | 49 |

| 5.4 Impact of Initial Population on Convergence            | 50 |

| 5.5 Testing the policies together                          | 52 |

| Chapter 6                                                  | 54 |

| Conclusion and Future Work                                 | 54 |

| 6.1 Conclusion                                             | 54 |

| 6.2 Future Work                                            | 55 |

| References                                                 | 57 |

# Chapter 1

## Introduction

| 1.1 Introduction | 1 |

|------------------|---|

| 1.2 Outline      | 4 |

|                  |   |

#### 1.1 Introduction

In the past decades, computers have evolved at a fast rate in terms of raw computing power, enabling unprecedented progress in nearly every field of science and technology. Faster processors, longer pipelines, more cores, and improved memory systems have all cumulatively enabled systems to become more powerful and efficient. In the meantime, however, while hardware has advanced, so have the demands put upon it, applications today manage increasingly large amounts of data and execute more complex logic, often with real-time or performance-sensitive constraints.

Two basic laws of computer architecture, Moore's Law and Amdahl's Law, have shaped performance progress expectations for decades. Both laws indicate a disturbing trend: historically, the pace of progress in general-purpose hardware is slowing. Physical limitations in transistor scaling, power constraints, and parallelization diminishing returns cause computational performance to plateau.

System designers must then concentrate on microarchitectural optimizations that make better use of what is available. One of the most impactful areas is the memory hierarchy, and in particular, cache memory systems. Of the many levels of cache, the Last-Level Cache (LLC) is central. Positioned directly in front of primary memory in the hierarchy, the LLC is a large, shared buffer that can absorb costly memory accesses if managed properly. Retrieving data from the LLC is significantly faster than retrieving it from DRAM and can eliminate hundreds of CPU cycles per access.

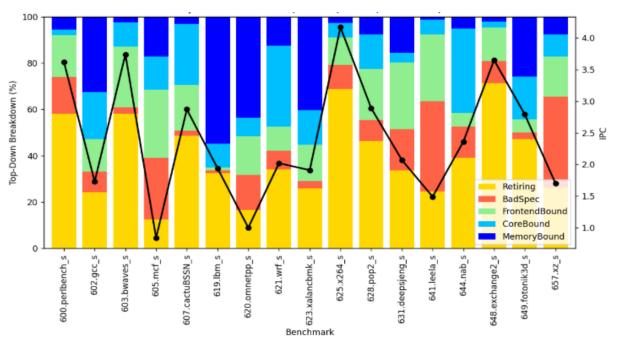

The benefits of the LLC rely mostly on how well it can store useful information. One key parameter that influences cache performance is its cache replacement policy (CRP). A CRP decides what data to remove from the cache when new data is to be brought into a full set of caches. Figure 1.1 illustrates how different benchmarks suffer from suboptimal CRPs, showing increased miss rates and lower IPC compared to workloads where the cache policy aligns better with the access behavior.

Figure 1.1: Breakdown of the Performance of SPEC CPU207 Workloads using top-down analysis

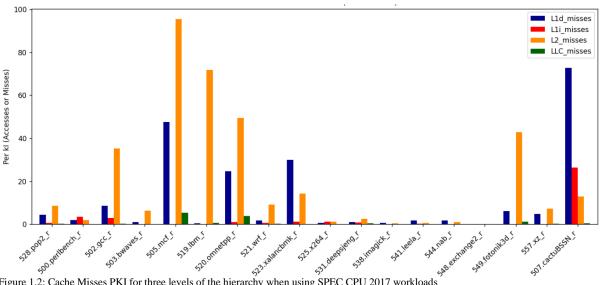

After looking at the benchmarks that recorded many cache misses (Figure 1.2), the results showed that what makes those benchmarks not perform so well was that they all had many LLC misses, demonstrating that having the optimal CRP for the LLC cache can really change its performance.

Figure 1.2: Cache Misses PKI for three levels of the hierarchy when using SPEC CPU 2017 workloads

Many systems use static cache replacement policies like Least Recently Used (LRU) and First-In-First-Out (FIFO). These policies are simple and easy to implement because they always follow the same fixed rules. However, they do not adjust to different workloads or changing access patterns, which means they can make poor decisions when the workload behaves differently. This has led to the development of adaptive policies, such as Dynamic Re-Reference Interval Prediction (DRRIP) [2], which attempt to dynamically switch between policies like SRRIP and BRRIP depending on runtime performance. While such solutions offer improvements, their adaptability is still limited to predefined options.

Another way of making the policies adaptive is using an optimization search, such as Genetic Algorithms (GAs), to find the optimal policy for a given workload [4]. Prior work [1] has shown that there are improvements over static policies like LRU and SRRIP, making GA search a relevant option to find the optimal policy.

In this work, genetic search is used to explore the design space of cache replacement policies by representing each policy as a set of functions, like where to insert a new data entry in the cache, or how to handle eviction. These decisions are different for all instruction types, like Loads, Request For Ownership, Writeback and Prefetching, to have a broader search space. This structured representation allows the genetic algorithm to systematically evolve and evaluate different combinations, effectively navigating the large policy space to discover those that yield the best performance for given workloads.

This thesis explores how the process of genetic search for cache replacement policies can be improved and extended to become more effective, flexible, and workload aware.

A central focus of this thesis is to explore the trade-off between two different optimization approaches: one where the cache replacement policy is tuned separately for each benchmark, and another where a single policy is chosen to perform well on average across all benchmarks. By comparing these two approaches, we can understand not just which method gives better performance but also learn more about the functions. Which are those functions that really made the difference for the policy to be optimal for its workload, and which functions might not matter as much. These insights can help guide the design of more flexible and effective cache replacement strategies in the future.

In addition, this thesis explores how many distinct policies are truly needed to achieve good performance across diverse workloads. Specifically, we investigate whether a small set of carefully chosen policies can cover the full spectrum of benchmarks, by selecting the right one for each case, rather than relying on a single general-purpose policy. These selected policies are later evaluated and compared against the single-best policies found for the same workload.

To answer these questions, this thesis combines the use of ChampSim, a state-of-the-art trace-driven simulator, and GeST, a genetic algorithm framework adapted to evolve and evaluate CRP configurations.

Throughout this thesis, several important observations emerged. First, we found that tuning policies for individual benchmarks consistently outperformed using a shared policy across all workloads. We also identified that insertion functions played a much more significant role in policy success than demotion functions. Another key finding was that starting the genetic search with a crossover point in the middle yields better results than a random crossover point. These insights support the idea that workload-aware and well-structured search strategies are essential for designing effective cache replacement policies.

#### 1.2 Outline

This thesis is structured into seven chapters. Chapter 1 introduces the research topic, motivation, and goals. Chapter 2 provides the necessary background on modern CPUs,

memory hierarchies, cache structures, genetic algorithms, and simulation tools, ending with related work and motivation. Chapter 3 explains SRRIP and DRRIP [2] cache replacement policies, including their limitations. Chapter 4 describes the experimental frameworks and methodology, including, GeST [5], ChampSim [6], and the genome encoding process. Chapter 5 presents workload-based experiments and analyzes policy behaviors. Chapter 6 focuses on experiments and their results involving dual-policy configurations. Finally, Chapter 7 concludes the thesis and outlines directions for future work.

# Chapter 2

# **Background**

| 2.1 Modern CPUs                  | 6  |

|----------------------------------|----|

| 2.1.1 Moore's Law                | 8  |

| 2.1.2 Amdahl's Law               | 9  |

| 2.2 Memory Hierarchy             | 10 |

| 2.2.1 Cache Memory               | 11 |

| 2.3 Cache Replacement Policies   | 13 |

| 2.4 Genetic Algorithm            | 15 |

| 2.5 Microarchitectural Simulator | 16 |

|                                  |    |

#### 2.1 Modern CPUs

CPUs of today are the backbone of nearly all computing equipment, from a lone notebook to massive data centers. They have evolved a great deal to become highly sophisticated pieces of technology that can run billions of instructions per second with ease. The increase in performance has been made possible through numerous innovations in instruction pipelines, microarchitecture, and memory hierarchies.

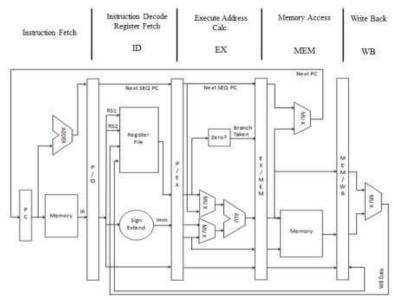

When a program runs, the CPU cycles through a sequence of operations:

- 1.Fetch: The next instruction is fetched from memory by the CPU.

- 2.Decode: The instruction is decoded and translated into signals that the CPU can interpret.

- 3.Execute: The CPU performs the operation needed, such as a calculation or logical operation.

- 4. Memory Access: The CPU accesses memory, if needed, to write or read data.

- 5. Write Back: The result of the operation is written to a register or written back to memory.

To make this process faster, modern processors rely on deep pipelines and multiple execution units so that they can run several instructions simultaneously.

Figure 2.1: The CPU Pipeline and its 5 stages

The pipeline ensures that we in a cycle, all 5 stages are active, instead of waiting for each instruction to go through all 5 operations and then proceeding with the next instruction. Between each 2 stages there is a pipeline register. These are crucial for maintaining the separation and synchronization between each stage of the instruction cycle. They hold the output of one stage and pass it as input to the next stage during the next clock cycle.

A limitation of the pipeline is the dependency between subsequent instructions, which slows down the execution potential. Among the most significant developments here is out-of-order execution, a technique that enables the CPU to perform instructions as and when their operands are ready, so it executes instructions that do not depend on each other, rather than precisely in the order they appear in the program. This increases instruction-level parallelism and avoids wasting time waiting on slower operations.

To help with this, CPUs also exploit parallelism at different levels. From the execution of independent instructions simultaneously within one core, to the execution of multiple threads across many cores, modern CPUs are designed to do more in less time. Simultaneous multithreading (SMT), or hyper-threading, is a function that allows one

physical core to execute more than one instruction stream, or thread, at the same time. This enhances use of available resources and enables improved multitasking.

#### 2.1.1 Moore's Law

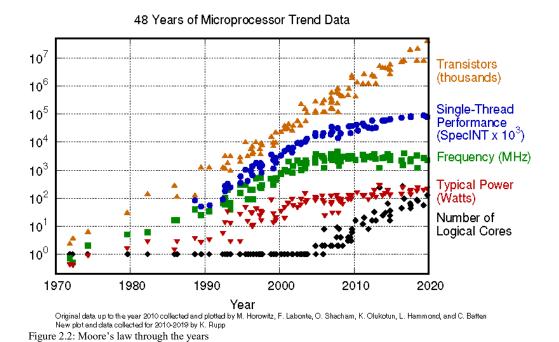

For many years, Moore's Law was an important principle in the semiconductor industry. Moore's law states that the number of transistors on an integrated circuit would double approximately every two years. This growth of transistors would mean increased computational power, allowing CPUs to become faster, smaller, and more energy-efficient with each new generation. For decades, software performance often improved simply by waiting for hardware to catch up—new processors would deliver better results without having to make big changes to the code or the system architecture.

However, in recent years, Moore's Law has shown signs of slowing down. Transistors are now approaching atomic-scale dimensions, which is very expensive, providing minimal benefits, due to issues such as overheating manufacturing complexity. These issues make it harder to maintain the historical pace of improvement. As a result, so t here needs to be smarter system design to manage the hardware.

From Figure 2.1.1 we can see that the single-thread performance and the clock frequency have found a bound, even with the transistor number increasing.

This slowdown has direct implications for system design. Rather than expecting hardware to solve performance bottlenecks, attention is now shifting toward microarchitectural and algorithmic optimizations. In this context, cache memory systems, especially the Last-Level Cache (LLC), play a crucial role. Efficient cache management helps bridge the performance gap between the CPU and main memory by keeping frequently accessed data closer to the processor.

The limitations imposed by the end of Moore's Law motivate the exploration of smarter cache replacement strategies. By using techniques like genetic algorithms to adapt and optimize replacement policies, the goal is to improve system performance through better use of existing hardware—rather than relying on future transistor scaling. This reflects a broader shift in computing, where intelligent resource management and data-aware algorithms are essential for extracting more performance from today's complex systems.

#### .1.2 Amdahl's Law

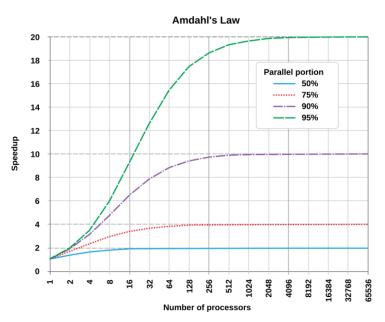

To break through the limitation of Moore's Law, parallel work on multiple cores became a growing trend. The reality is that even parallelism has limits. Amdahl's Law in parallel computing reminds us that program speedup is limited by the portions that can't be parallelized.

Figure 2.3: Amdahl's Law speedup limitation

No matter how many cores a processor has or how fast they run, there will always be bottlenecks, serial segments of code or system overheads, that cap overall performance.

This law reminds us of a valuable fact: it takes more than just adding hardware if the architecture and algorithms don't use it efficiently. This means that we must consider improving single-thread performance, so even if there are serial parts of a program, we optimize those periods with the right algorithm. One of the ways is to optimize cache behavior, i.e., the LLC, because it matters most to how many cycles an instruction will execute.

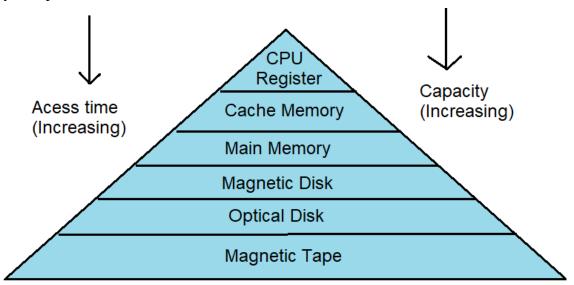

## 2.2 Memory Hierarchy

Modern computer systems utilize a hierarchical memory architecture designed to balance speed, capacity, and cost. As we move from the processor toward lower levels of the memory hierarchy, culminating in main memory and persistent storage, each level typically offers increased capacity but also higher access latency. This latency is measured in CPU cycles, and delays at lower levels can significantly impact overall system performance.

Figure 2.4: The memory Hierarchy

To mitigate the high cost of frequent main memory accesses, most modern processors incorporate a multi-level cache system, consisting of L1, L2, and Last-Level Cache (LLC). The L1 cache is the smallest but fastest, located closest to the CPU core. If data is not found in L1, the processor checks the L2 cache, which is larger but slower. Failing

that, it proceeds to the LLC, which is shared across cores and offers even more capacity at the cost of further increased latency.

This tiered caching strategy ensures that frequently accessed data and instructions are kept as close to the CPU as possible, reducing cache miss rates and significantly decreasing the number of costly main memory accesses. As a result, the memory hierarchy plays a critical role in maintaining high performance in modern computing systems.

#### 2.2.1 Cache Memory

A typical cache is made up of fixed-length blocks known as cache lines, usually 64 bytes per line. Such lines are grouped into sets, and the number of cache lines per set determines the cache associativity. The general structure of the cache, the manner in which it stores data and retrieves data—strongly affects performance and ease of implementation.

There are three primary structures for the cache:

- Direct-Mapped Cache: Each memory block maps to a specific cache line using the lower bits of its address. It's fast and simple but prone to conflict misses, where multiple blocks compete for the same line.

- Fully-Associative Cache: A block can be stored in any cache line, reducing conflict misses. However, this requires checking all tags on each access, increasing hardware complexity and access time. It's mainly used in small caches like the TLB.

- Set-Associative Cache: Common in modern systems, this structure divides the cache into sets, each containing multiple lines (ways). A block maps to a specific set but can occupy any line within it. It offers a good balance between performance and complexity, reducing conflict misses more effectively than direct-mapped caches without the overhead of fully-associative designs.

When a CPU reads from memory, the memory address is divided into three components:

- Offset: Determines the specific byte within a cache line.

- Index: Chooses the set in the cache to look for.

- Tag: To find out if the data being looked for is available in the chosen set.

The tag is used by the CPU to look up the correct set to determine whether the data is present, a cache hit or not, a cache miss. Each line has a valid and a dirty bit. A valid bit tells us if the data in there is meaningful or not, in most cases a valid bit of 0 indicates a cold cache. The dirty bit is used for write-back caches to indicate that the value has changed and when the block will be evicted, it needs to update the main memory with the new value. On a hit, the data is retrieved with minimal latency. On a miss, the block must be retrieved from a lower level in the hierarchy (e.g., L2, LLC, or main memory), which is much more costly in terms of latency. There are generally 3 types of cache misses:

- Cold Miss: At start of a program, there is an empty cache. Cold misses are mandatory misses. They cannot be avoided even with infinite memory.

- Capacity Miss: A miss when cache cannot store all the data required.

- Collision Miss: Even with enough space, there are misses because the entries go

to the same cache line, bad usage of associativity (mostly direct mapped or 2-way

associativity)

In the instance of a capacity cache miss, when a new block has to be brought into memory, the system must determine which block should be replaced. The choice of replacement is according to the cache replacement policy (section 2.3). How good a policy is impacts cache hit rates and system performance directly. A good policy works by attempting to estimate which of the blocks won't be needed soon, in turn retaining the highly temporally local blocks.

In the context of cache, not all memory accesses are the same. There are 4 key instruction types, Load, Request for Ownership (RFO), Prefetch, and Writeback. These types are distinct from others (such as control instructions or computation-focused

operations) because they directly interact with the memory hierarchy and influence what data enters or updates the cache. Load instructions fetch data from memory for read operations and are often performance-critical. RFOs are triggered during write operations that require exclusive access to a cache line, impacting both coherence and placement decisions. Prefetches are speculative loads issued in advance to reduce future latency; while they can improve performance, they also risk polluting the cache if mispredicted. Writebacks occur when dirty data is evicted and must be written to memory—these accesses do not typically bring data into the cache, but they still affect replacement logic.

The design and optimization of such policies, particularly at the Last-Level Cache (LLC), where misses are most expensive, is essential. By seeking adaptive and intelligent eviction policies, we aspire to improve data persistence in cache and reduce reliance on slow main memory access.

## 2.3 Cache Replacement Policies

Cache Replacement Policies (CRP) are algorithms that decide on which cache block to evict in a line, in the case of a cache miss. The target of CRP is to reduce memory access time, done in two ways:

- Increase hit rate

- Decrease latency

Improving one often comes at the expense of the other. For instance, a policy that aggressively retains frequently used blocks may increase the hit rate but also introduce delays in decision-making and complexity in replacement logic.

The optimal cache replacement policy is the one that can predict which block, out of all the blocks, will be requested the latest in future cache accesses. That's known as Belady's Optimal algorithm and is impossible to achieve, since nobody can see into the future. Modern cache replacement policies try to predict which block is best to be evicted, through various techniques.

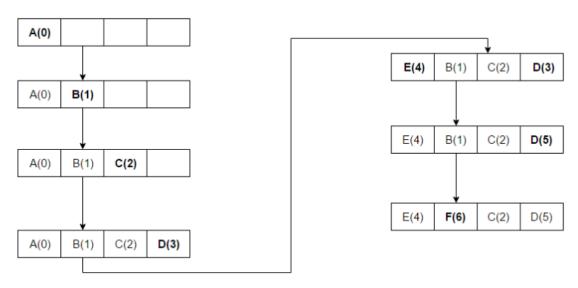

A policy that is widely used even today is LRU (Least Recently Used). LRU tracks previous entries in the cache and in case where all blocks are full, removes the one that was accessed the longest time ago.

Figure 2.5: The LRU Policy

In the example above, we see that after each entry, each block has a number assigned to it, to keep track of when it was used. On a cache hit, all the numbers need to be updated, since the recency of each block changes, the one that was accessed becomes the most recently used element, and the other get an increment of +1 meaning they are least recently used than before. Computer systems use PLRU, which is a model that acts like LRU in most cases, but has significantly better hardware overhead. Traditional LRU needs  $log_2(N)$  bits per block, meaning  $nlog_2(N)$ , considering N-way associativity (for n=4 in the example above, each block requires 2 bits to track the position from 0 to 3, whereas PLRU only needs N-1 bits per set, making it more hardware efficient. This means that for a good cache replacement policy, hardware complexity is also a very important factor.

### 2.4 Genetic Algorithm

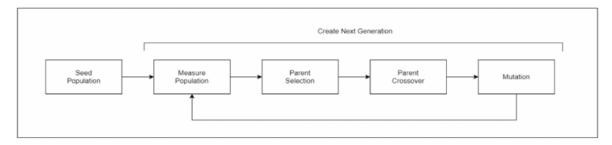

With so many cache replacement policies, a big search space is created in the attempt to find which policy suits a workload best. To solve this, we propose Genetic Algorithms (GAs). Genetic Algorithms are a class of search and optimization algorithms inspired by the natural process of selection and biological evolution. They belong to the broader family of evolutionary algorithms, which work best in solving complex problems with vast and ill-defined solution spaces where traditional optimization techniques are not adequate.

Essentially, genetic algorithms operate on a set of solution candidates, generally referred to as individuals or chromosomes. These individuals are all evaluated using a fitness function, where the fittest individuals (the ones with strongest genes) pass on to the next generation, while creating new individuals with traits from two of the fittest individuals. In Figure 2.4, we can see the workflow of a typical genetic algorithm.

Figure 2.6: Genetic algorithm workflow

The steps that a genetic algorithm takes are explained as follows:

- Seed Population: In the start, we start with random individuals.

- Measure Population (Fitness Function): Every individual is evaluated through a

fitness function that measures how well it performs towards the goal at hand. It is

the natural analogue of survival of the fittest.

- Selection: Fitter organisms will be more likely to be selected for reproduction.

Roulette wheel, tournament selection, and rank selection are the most widely used selection methods. In the experiments in this thesis, tournament selection is used.

- Crossover: Two chosen individuals are merged and parts of their genomes are exchanged to produce new individuals with traits from both parents. This generates diversity and allows beneficial traits to be passed on.

- Mutation: With a very small probability, random changes are applied to individual genes. Mutation maintains the genetic diversity of the population at the highest level and prevents converging too early to the suboptimal solution.

- Replacement: The new individuals are created, ready to be evaluated by the fitness

algorithm. This process repeats until we reach the number of generations

conFigured by the user.

Despite their versatility, applying genetic algorithms to cache replacement introduces certain challenges, most notably, how to accurately and efficiently encode a policy as a genome. The design of the fitness function and the representation of policy functions greatly influence the algorithm's success. Nevertheless, given the immense search space of potential policy configurations, GAs provide a promising foundation for discovering high-performing strategies tailored to specific workloads. This motivates our use of evolutionary techniques in this thesis (see Section 2.6.2) and leads to our proposed encoding framework in Section 4.3.2.

#### 2.5 Microarchitectural Simulator

Microarchitectural Simulators give us the opportunity to emulate the behavior of a microarchitecture, by configuring many properties such as: memory size for all hierarchical levels, the branch prediction type and most importantly, the cache replacement policy to be used. This is very important for this thesis, since we are trying to run different experiments with a big variety of cache replacement policies, making it impossible to use real hardware. Microarchitectural Simulators are useful to test on what changes would be beneficial for a microarchitecture before applying them in practice. For the purpose of this thesis, ChampSim [6] (section 4.2) to run our simulations with different cache replacement policies, so we can evaluate each policy.

# Chapter 3

#### **SRRIP-DRRIP**

| 3.1 SRRIP                | . 17 |

|--------------------------|------|

| 3.2 Set Dueling          | . 19 |

| 3.3 DRRIP                | . 20 |

| 3.4 Improving upon DRRIP | . 21 |

|                          |      |

#### 3.1 SRRIP

On the talk of cache replacement policies, LRU works generally well, but it faces a big issue on some workloads, specifically on workloads with scans. Scans are data streams that are loaded/used only once. These types of workloads, when they are inserted into the cache, they get the MRU (Most recently used) position, even though they will never be accessed again, meaning that many entries that would be used later, are evicted, while cache stays polluted with such bad entries. An algorithm that would work well in this workload is MRU, which has the same logic as LRU, but instead of evicting the least recently used block, it evicts the most recently used block. This policy is scan-resistent, so it handles scans very well. The problem is that for any other workload, it has a very bad performance.

SRRIP [2] is a scan-resistant cache replacement policy that outperforms LRU, while being scan-resistant. SRRIP uses a counter of M bits for each block in the set, called Rereference Prediction Value (RRPV), which predicts if a cache block will be re-used. An RRPV value of 0 indicates that the block will be reused in the very near future, while a value of 2<sup>M</sup>-1 (we consider M=2 for the examples below, since it performs the best) indicates that the block will be reused in the distant future, essentially saying that the block should be evicted from the cache. The SRRIP algorithm works as follows:

#### On Cache Hit:

1. Set the RRIP value of the accessed block to 0.

#### On Cache Miss:

- 1. Search for the first block with RRIP value of 3.

- 2. If found, replace the block.

- 3. If not found:

- a. Increment the RRIP values of all blocks.

- b. Repeat the search for the first block with RRIP value of 3.

#### On Insertion:

1. Set RRPV value to 2.

|                       | Cache Hit: (i) move block to MRU  Cache Miss: (i) replace LRU block (ii) move block to MRU | Cache Hit: (i) set nru-bit of block to '0'  Cache Miss: (i) search for first '1' from left (ii) if '1' found go to step (v) (iii) set all nru-bits to '1' (iv) goto step (i) (v) replace block and set nru-bit to '1' | Cache Hit: (i) set RRPV of block to '0'  Cache Miss: (i) search for first '3' from left (ii) if '3' found go to step (v) (iii) increment all RRPVs (iv) goto step (i) (v) replace block and set RRPV to '2'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | (a) LRU                                                                                    | (b) Not Recently Used (NRU)                                                                                                                                                                                           | (c) 2-bit SRRIP with Hit Promotion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | $a_2 \rightarrow a_1 \rightarrow b_4 \rightarrow b_3$                                      | b <sub>3</sub> 0 b <sub>4</sub> 0 a <sub>1</sub> 0 a <sub>2</sub> 0  "nru-bit"                                                                                                                                        | (a <sub>1</sub> ) 0 (a <sub>2</sub> ) 0 (b <sub>3</sub> ) 2 (b <sub>4</sub> ) 2 (**RRPV**                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <i>a</i> <sub>2</sub> | $a_1 \rightarrow b_4 \rightarrow b_3 \rightarrow b_2$ miss                                 | $\begin{bmatrix} b_3 \end{bmatrix}_0 \begin{bmatrix} b_4 \end{bmatrix}_0 \begin{bmatrix} a_1 \end{bmatrix}_0 \begin{bmatrix} b_2 \end{bmatrix}_1$ miss                                                                | a <sub>1</sub> 0 a <sub>2</sub> 1 b <sub>3</sub> 2 b <sub>4</sub> 2 hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $a_I$                 | $b_4 \rightarrow b_3 \rightarrow b_2 \rightarrow b_1$ miss                                 | $\begin{bmatrix} b_3 \end{bmatrix}_0 \begin{bmatrix} b_4 \end{bmatrix}_0 \begin{bmatrix} b_1 \end{bmatrix}_1 \begin{bmatrix} b_2 \end{bmatrix}_1$ miss                                                                | $a_1$ $a_2$ $a_3$ $a_4$ $a_5$ |

| $b_4$                 | $b_3 \rightarrow b_2 \rightarrow b_1 \rightarrow a_1$ miss                                 | $b_3$ $0$ $a_2$ $1$ $b_1$ $1$ $b_2$ $1$ miss                                                                                                                                                                          | $a_1$ $a_2$ $a_3$ $a_4$ $a_5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| b <sub>3</sub>        | $b_2 \rightarrow b_1 \rightarrow a_1 \rightarrow a_2$ miss                                 | $a_1 \ 0 \ a_2 \ 0 \ b_1 \ 0 \ b_2 \ 0$ miss                                                                                                                                                                          | $a_1 \ 0 \ a_2 \ 0 \ b_1 \ 2 \ b_2 \ 2 \ miss$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| b <sub>2</sub>        | $b_1 \rightarrow a_1 \rightarrow a_2 \rightarrow 1$ miss                                   | $a_1 \ 0 \ a_2 \ 0 \ b_1 \ 0 \ I \ 1 $ miss                                                                                                                                                                           | $a_{l}$ $0$ $a_{2}$ $0$ $b_{l}$ $0$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $b_I$                 | $a_1 \rightarrow a_2 \rightarrow 1 \rightarrow 1$ miss                                     | $a_1$ $0$ $a_2$ $0$ $1$ $1$ $1$ $miss$                                                                                                                                                                                | $a_1$ $0$ $a_2$ $0$ $1$ $3$ $1$ $3$ miss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $a_I$                 | $a_2 \rightarrow a_1 \rightarrow 1 \rightarrow 1$ hit                                      | $a_1$ $0$ $a_2$ $0$ $1$ $1$ $1$ $1$ hit                                                                                                                                                                               | a <sub>1</sub> 2 a <sub>2</sub> 0 I 3 I 3 hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| a <sub>2</sub>        | $a_2 \rightarrow a_1 \rightarrow 1 \rightarrow 1$ hit                                      | a <sub>1</sub> 0 a <sub>2</sub> 0 I 1 I hit                                                                                                                                                                           | a <sub>1 2</sub> a <sub>2 2</sub> I <sub>3</sub> I <sub>3</sub> hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| a <sub>2</sub>        | $a_1 \rightarrow 1 \rightarrow 1 \qquad miss$                                              | a <sub>I</sub> 0 I 1 I 1 I miss                                                                                                                                                                                       | a <sub>1</sub> 2 I 3 I 3 I 3 miss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Ref<br>a <sub>I</sub> | ↓ ↓ ↓ ↓ ↓ miss                                                                             | $\Box_1 \Box_1 \Box_1 \Box_1 \Box_1$ miss                                                                                                                                                                             | I 3 I 3 I 3 miss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Next                  | RRIP head RRIP tail                                                                        |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 3.1: SRRIP compared to LRU and NRU

To better understand what makes SRRIP scan resistant and better than LRU, we consider the example shown in Figure 3.1. A steam of accesses on b1, b2, b3 and b4 are sent to the cache, and after there are normal accesses of frequent data like before the stream (a1 and a2). SRRIP is compared to LRU and NRU (which is SRRIP with M=1, showcasing how the M value is important to the policy being scan-resistant). We see that both LRU and MRU struggle to keep a1 and a2 inside the cache, but due to SRRIP inserting with RRPV 2 and by the way it handles eviction, we can see it keeps frequently accessed data, even after a sudden scan. It has to be noted that SRRIP works the same on all access types. In

later chapters we will see, that we can modify SRRIP to have a different behavior on these 4 different access types:

- Load: A read instruction that asks the CPU to get data from memory. If the data isn't in the cache, it causes a cache miss.

- RFO (Request For Ownership): Happens before a write. It asks for exclusive access to a cache line so the CPU can safely modify it.

- Prefetch: Tries to bring data into the cache before it is actually needed. It can help performance, but if the data isn't used, it wastes space.

- Writeback: Happens when changed data is removed from the cache and saved back to main memory. It doesn't fetch new data, but it still takes up a cache line and affects replacement decisions.

## 3.2 Set Dueling

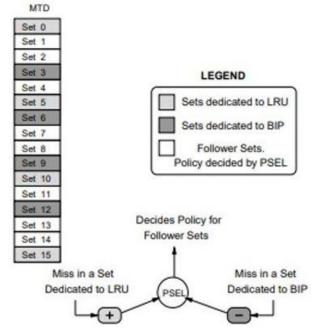

While SRRIP performs well in workloads with scans, SRRIP still possesses a big issue. SRRIP performs bad with thrashing, which is a situation where constantly loading and evicting data entries of the working set, without keeping some of the working set data in the cache, caused when the working set is larger than cache. Also SRRIP is a static policy, which means that it does not have an adaptation system to the workload, it always performs the same steps, given all workloads. Set dueling [3] looks to fix this issue, by creating an environment where two policies can run at the same time, so the policy that best fits the current instruction sequence will be executed. Set dueling dedicates some sets (16 to 32) to each of the 2 policies, called the leader sets. So the leader sets will be always running one policy and evaluating it for the other sets (follower sets). We keep track of a counter called PSEL. PSEL is a saturating counter that keeps track of which of the two competing policies incurs fewer misses, one policy adds to the counter and the other subtracts if a miss occurs in the sets dedicated to it. The most significant bit of the counter determines the policy that performs better. Figure 3.2 illustrates how Set Dueling will work with LRU and BIP as competing policies.

Figure 3.2: Set Dueling Mechanism on LRU and BIP

#### 3.3 DRRIP

To make use of Set Dueling and provide a Thrash-resistant policy to help SRRIP with those workloads, BRRIP is proposed. BRRIP works by inserting with an RRPV value of 3 with a small probability of inserting with RRPV value 2. In thrashing scenarios, the working set is too large to fit in cache, and new data constantly replaces existing blocks. SRRIP might keep bringing in blocks that don't get reused, mistakenly giving them midterm life and evicting more useful blocks .BRRIP, by contrast, treats most new blocks as likely trash, so it protects existing blocks longer—only admitting new entries cautiously. This results in fewer useful blocks being evicted prematurely, making BRRIP more resilient to cache pollution during thrashing.

Combining them together with set-dueling, we get DRRIP. DRRIP successfully combines the strengths of SRRIP and BRRIP by using Set Dueling to dynamically select the better-performing policy based on runtime behavior. This adaptability makes DRRIP effective across a wide range of workloads, balancing between scan-resistant and thrash-resistant behavior. However, despite its success, DRRIP remains a heuristic-based solution that

may struggle with workloads exhibiting more complex or mixed access patterns. As such, there is still an opportunity to improve cache replacement performance by developing more adaptive and learning-based techniques, this is explored in the next section.

### 3.4 Improving upon DRRIP

While DRRIP is a self-switching cache replacement policy between SRRIP and BRRIP, it still is stuck between those two specific policies, SRRIP and BRRIP. That is, DRRIP can never switch to another policy or even a custom version of SRRIP for a specific workload. For example, a workload might benefit from a policy that inserts into a different position or sells blocks differently on reuse. DRRIP can't do that because it's married to SRRIP and BRRIP.

In a recent study [4], the use of Genetic Algorithms (GA) to optimize tree-based Pseudo-LRU (PLRU) caches was studied. In that study, GA was used to discover enhanced insertion and promotion rules that improved performance on specific workloads. That showed that using an evolutionary approach like GA can be useful to discover new cache policies that capture the scope more than fixed policies.

Based on that idea, this thesis takes the use of genetic algorithms one step further, by refining how genetic search is executed and what it can tell us. Rather than simply searching for the best policy, we examine the performance of the search under different workload configurations, i.e., how results change when optimizing for a single benchmark vs. averaging across many benchmarks. This helps us identify whether workload structure affects what the GA learns. In addition, we study which components of a cache replacement policy contribute the most to good performance and which components contribute the least, knowledge that can be used to streamline or guide future designs. Finally, we study how many different policies are truly needed to deliver optimal performance for all workloads, and whether a small, well-designed subset can beat out a single general-purpose solution. These guidelines are designed to make the genetic search process not only more effective, but also more comprehensible and adapable to diversity in actual use.

# Chapter 4

# Frameworks and Methodology

| 4.1 HPC System                        | . 22 |

|---------------------------------------|------|

| 4.2 ChampSim                          | . 23 |

| 4.2.1 Cache Configuration             | . 23 |

| 4.3 GeST                              | . 24 |

| 4.3.1 The framework                   | . 24 |

| 4.3.2 Configuring policies as genomes | . 26 |

| 4.4 SPEC 2017 Benchmarks              | . 30 |

| 4.4.1 The benchmarks                  | . 30 |

| 4.5 Evaluation Methodology            | . 32 |

|                                       |      |

## 4.1 HPC System

The experiments were carried out on a high-performance computing (HPC) platform located at the University of Cyprus. The platform is equipped with Intel® Xeon® Gold processors with a base frequency of 2.90 GHz. The platform has a dual-socket configuration with 32 physical cores in total, which is extremely appropriate for parallel computation. For the purpose of our research we will be running every experiment on a single core, while running many experiments across multiple cores, 1 per core. The operating system deployed is CentOS Linux, release 7.8.2003, providing a sTable and efficient platform upon which to run the high-level simulations required under this research. This powerful infrastructure was key to allowing the testing and evaluation of several cache replacement policies.

### 4.2 ChampSim

To evaluate candidate cache replacement policies in a controlled and realistic scenario, this thesis uses ChampSim [6], a trace-driven microarchitectural simulator specifically created for cutting-edge CPU and cache research. ChampSim is used throughout the academic and research community, serving as the testbed for a variety of large-scale competitions such as the 3rd Data Prefetching Championship (DPC3) and the 2nd Cache Replacement Championship (CRC2). Its extensible and modular design makes it especially well-suited to microarchitectural experimentation with functions such as branch predictors, prefetchers, and most importantly for this thesis, Last-Level Cache (LLC) replacement policies.

#### 4.2.1 Cache Configuration

For our experiments we modeled a 1-core out-of-order processor with 3 levels of cache. The configuration used is described in Table 4.1. For the LLC replacement policy, we used a modular version of DRRIP replacement policy, configured to have the same policy switch between set-dueling, for running with single policies, and modified to set-duel between two policies for the last experiment. For all the simulations, we ran 100 million warm-up instructions, and 500 million execution instructions.

| Parameter            | Configuration              |

|----------------------|----------------------------|

| L1 I-Cache (Private) | 32KB, 64B blocks, 8-way    |

|                      | 8 MSHRs, 1 cycle latency   |

|                      | LRU Replacement Policy     |

| L1 D-Cache (Private  | 32KB, 64B blocks, 8-way    |

|                      | 8 MSHRs, 4 cycles latency  |

|                      | LRU Replacement Policy     |

|                      | Next-Line Prefetcher       |

| L2 Cache (Private)   | 256KB, 64B blocks, 8-way   |

|                      | 16 MSHRs, 8 cycles latency |

|                    | LRU Replacement Policy           |  |

|--------------------|----------------------------------|--|

|                    | IP-Based Stride Prefetcher       |  |

| LLC Cache (Shared) | 2MB per core, 64B Blocks, 16-way |  |

|                    | 32 MSHRs, 20 cycles latency      |  |

|                    | Modular DRRIP-Based Replacement  |  |

|                    | Policy                           |  |

| Branch Predictor   | Perceptron                       |  |

Table 4.1: ChampSim Cache Configuration

#### **4.3 GeST**

#### 4.3.1 The framework

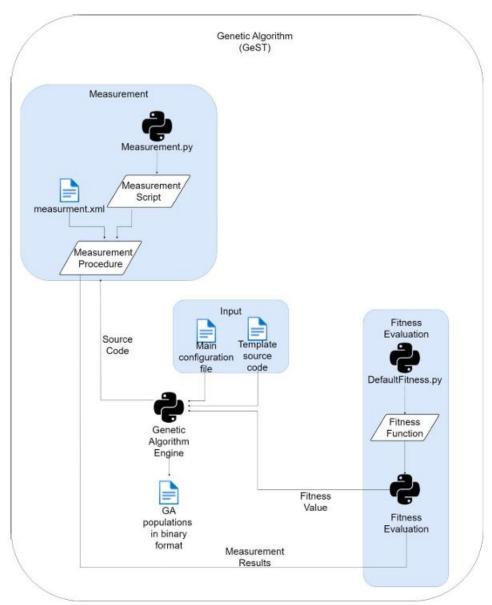

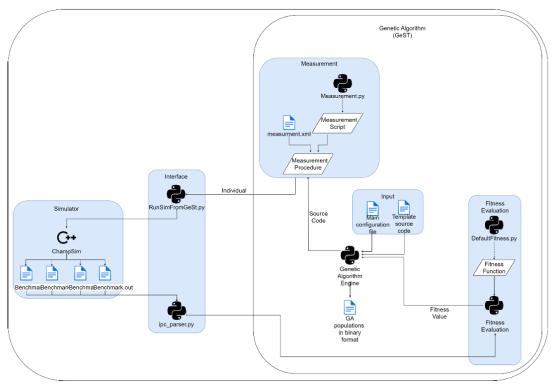

In this research, we utilize GeST [5] (Generator for Stress-Tests), which is a framework to automatically generate CPU stress tests using genetic algorithms. GeST is designed for the exploration of the effect of instruction-level workloads on processor performance and can target single microarchitectural structures such as functional units, the cache hierarchy, or the CPU pipeline to stress. GeST is modular by design and very flexible, and thus perfectly suitable for both cache behavior studies and replacement policy investigations.

The framework operates by evolving a population of candidate stress tests over a number of generations. Each individual in the population is a loop of assembly instructions, with the goal of placing high computational or memory pressure on the processor. The individuals are compiled and executed, and a fitness function, defined by the user, evaluates their performance in terms of instruction-per-cycle (IPC) or voltage fluctuation. In this dissertation, we modify the individual to be a cache replacement policy configuration, further explained in section 4.3.2, while changing the fitness function to be on speedup over a baseline LRU IPC. The evolution process follows standard genetic algorithm procedures: the fittest individuals are selected to reproduce the next generation, their instruction sequences are merged through crossover, and slight random changes are

introduced through mutation to ensure diversity and search space exploration. Figure 4.1 shows the overview of GeST.

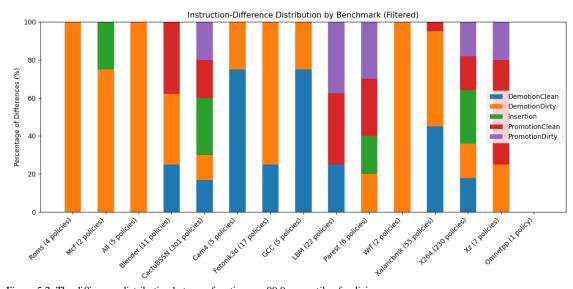

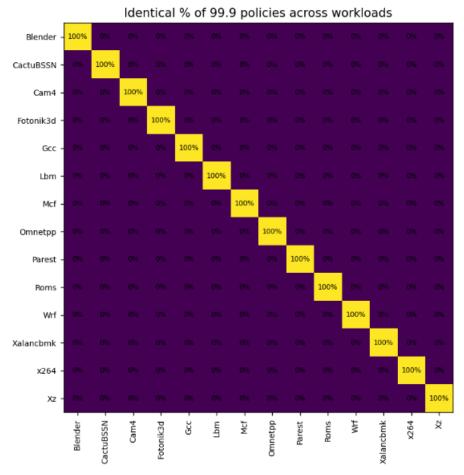

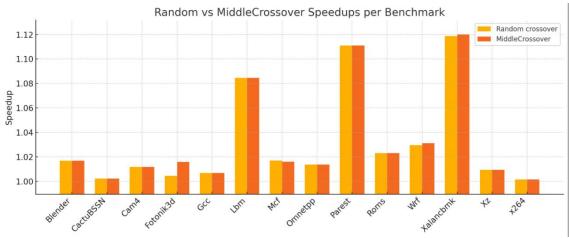

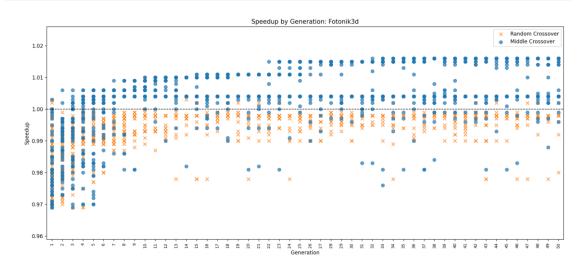

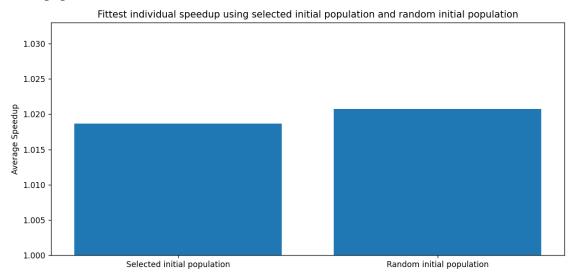

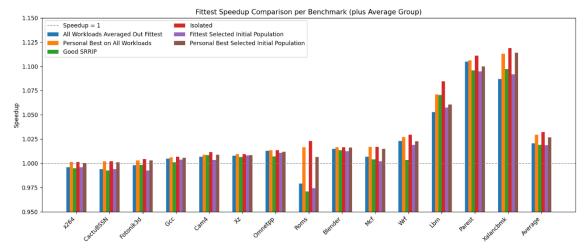

Figure 4.1: The GeST Framework